#### US006468160B2

# (12) United States Patent Eliott

## (10) Patent No.: US 6,468,160 B2

(45) **Date of Patent:** \*Oct. 22, 2002

### 54) SECURITY SYSTEM FOR VIDEO GAME SYSTEM WITH HARD DISK DRIVE AND INTERNET ACCESS CAPABILITY

### (75) Inventor: Scott Eliott, Redmond, WA (US)

(73) Assignee: Nintendo of America, Inc., Redmond,

WA (US)

(\*) Notice: This patent issued on a continued prosecution application filed under 37 CFR

1.53(d), and is subject to the twenty year patent term provisions of 35 U.S.C.

154(a)(2).

Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 50 days.

(21) Appl. No.: 09/384,189

(22) Filed: Aug. 27, 1999

(65) **Prior Publication Data**

US 2002/0077177 A1 Jun. 20, 2002

### Related U.S. Application Data

- (63) Continuation-in-part of application No. 09/288,293, filed on Apr. 8, 1999.

- (51) **Int. Cl.**<sup>7</sup> ...... **A63F 13/12**; A63F 13/00

### (56) References Cited

### U.S. PATENT DOCUMENTS

4,247,106 A 1/1981 Jeffers et al. 4,299,386 A 11/1981 Kulesza et al. 5,251,909 A 10/1993 Reed et al.

(List continued on next page.)

#### OTHER PUBLICATIONS

Henry, "Local Company Big Player in Electronic Games", *The Sun*, Baltimore, MD., Nov. 1, 1998, 3 pages.

Freier et al., "The SSL Protocol Version 3.0", Transport Layer Security Working Group, Internet—Draft, http://cuisung.unige.ch/memories/Hugentobler/draft302.txt.gz., Nov. 1996.

WebTV Networks, Inc. webtv http://www.WebTV.net, all pages, Jan. 2000.

Primary Examiner—Michael O'Neill (74) Attorney, Agent, or Firm—Nixon & Vanderhye P.C.

### (57) ABSTRACT

An existing video game system is modified to include additional communication and storage capability via a modem and hard disk drive. In accordance with one embodiment of the present invention, the primary system security features are incorporated into a video game system expansion device having a hard disk drive. The security system does not rely on the relatively insecure video game system. The present exemplary embodiment focuses security control in a disk drive/mass media controlling engine which is physically disposed within the expansion device housing as close as possible to the hard disk drive and the downloaded video games and other data it is designed to protect. Security features are incorporated into, for example, a disk drive controlling processing engine to provide security features which extend far beyond simplistic password systems which have heretofore been utilized in conjunction with disk drive controllers. In accordance with an exemplary embodiment of the present invention, the disk controller also incorporates an encrypting engine which encrypts in accordance with a highly secure encrypting algorithm. A further level of security is provided in the illustrative embodiments by partitioning the hard drive into various partitions whose security/ accessibility is tightly controlled. Each application program, e.g., a video game, has a predetermined number of private partitions, including a read only encrypted partition.

### 99 Claims, 26 Drawing Sheets

# **US 6,468,160 B2**Page 2

| U.S. PATENT                                                                                                                                                                                        | DOCUMENTS                                                                              |                                                                                                                                                                                          | Waters et al.                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5,313,303 A 5/1994<br>5,350,176 A 9/1994<br>5,481,542 A 1/1996<br>5,497,479 A 3/1996<br>5,538,255 A 7/1996<br>5,558,339 A 9/1996<br>5,624,316 A 4/1997<br>5,630,757 A 5/1997<br>5,668,950 A 9/1997 | Ersoz et al. Hochstein et al. Logston et al. Hornbuckle Barker Perlman Roskowski et al | 5,923,379 A 7/1999 6,018,712 A * 1/2000 6,018,720 A * 1/2000 6,022,274 A 2/2000 6,033,316 A * 3/2000 6,055,314 A * 4/2000 6,097,441 A 8/2000 6,180,420 B1 * 8/2000 6,169,976 B1 * 1/2001 | Waters et al.         Patterson         Pactong       705/1         Fujimoto       705/26         Takeda et al.       380/25         Spies et al.       380/21         Allport       Larose et al.       380/4         Colosso       705/59         Cohen       705/59 |

| 5,762,555 A 6/1998                                                                                                                                                                                 | Bakoglu et al. Crump et al. Crump et al.                                               | 6,330,670 B1 12/2001<br>* cited by examiner                                                                                                                                              | England et al.                                                                                                                                                                                                                                                         |

Fig. 8

Oct. 22, 2002

| NAME                          | R/W | DESCRIPTION                                    |

|-------------------------------|-----|------------------------------------------------|

| DISK STATUS                   | R   | READ: DISK STATUS                              |

| LBA WRITE                     | W   | WRITING TO THIS ADDRESS CAUSES THE CONTENTS    |

| ADDRESS                       | **  | OF THE SECTOR BUFFER TO BE WRITTEN TO THE      |

| ADDITESS                      |     | LBA POINTED TO BY THIS LBA WRITE ADDRESS.      |

|                               |     | THE BUFFER COUNTER IS RESET.                   |

| LBA READ                      | W   | WRITING TO THIS ADDRESS CAUSES THE CONTENTS    |

| ADDRESS                       | **  | OF THE LBA POINTED TO BY THIS LBA READ ADDRESS |

| ADDITEOU                      |     | TO BE READ INTO THE SECTOR BUFFER.             |

|                               |     | THE BUFFER COUNTER IS RESET.                   |

| 1 <sup>2</sup> C S0' OWN      | R/W | ES0=0                                          |

| ADDRESS REGISTER              |     | READ/WRITE: OWN ADDRESS                        |

| 1 <sup>2</sup> C S0 DATA      | R/W | ES0=1                                          |

| REGISTER                      | i   | READ/WRITE: 1 <sup>2</sup> C DATA              |

| 1 <sup>2</sup> C S1 CONTROL   | R/W | READ: STATUS                                   |

| STATUS REGISTER               |     | WRITE: CONTROL                                 |

| 1 <sup>2</sup> C S2 CLOCK     | R/W | READ/WRITE: CLOCK SCALE VALUE                  |

| REGISTER                      |     |                                                |

| 1 <sup>2</sup> C S3 INTERRUPT | R/W | ES0=0: READ/WRITE: INTERRUPT VECTOR            |

| VECTOR                        | R   | ES0=1: READ: INTERRUPT VECTOR ACK CYCLE        |

| MODEM IN                      | R   | READ: MODEM STATUS & DATA                      |

| MODEM OUT                     | R/W | WRITE MODEM DATA                               |

|                               |     | READ MODEM OUT STATUS                          |

| MODEM OUT                     | W   | SEPARATE REGISTER TO CONTROL MODEM             |

| CONTROL                       |     | WRITE FUNCTIONS                                |

|                               | R/W | 512 BYTE SECTOR BUFFER FOR THE HARD DRIVE.     |

|                               |     | THE POINTER INTO THIS BUFFER IS INCREMENTED BY |

| SECTOR BUFFER                 |     | FOUR BYTES EACH TIME THE BUFFER IS READ OR     |

|                               |     | WRITTEN. AFTER 512 BYTES ARE ACCESSED THE      |

|                               |     | POINTER WRAPS AROUND.                          |

| VIDEO/INTERCAST<br>SPACE      | R/W |                                                |

|                               | R/W | READ: EXPANSION DEVICE SUPPORTS A SINGLE,      |

|                               |     | 32 BIT INTERRUPT STATUS REGISTER FOR THE       |

| INTERRUPT STATUS              |     | VIDEO GAME SYSTEM. VARIOUS BITS WILL BE        |

| REGISTER                      |     | ALLOCATED TO PROCESSES AS NEEDED DURING        |

|                               |     | DESIGN. WRITE: INTERRUPT MASK                  |

|                               |     |                                                |

|                               | ļ   |                                                |

Fig. 9

| FUNCTION                   | INT |

|----------------------------|-----|

| MODEM DATA IN READY        | Υ   |

| MODEM SEND READY           | Υ   |

| RTC ALARM                  | Υ   |

| I <sup>2</sup> C INTERRUPT | Υ   |

| INTERCAST                  | Υ   |

| DISK READ DATA READY       | Υ   |

| DISK WRITE COMPLETED       | Υ   |

| COUNTER AT 0               | N   |

FIG. 12

FIG. 14

## **BoxIDPacket**

| BoxID | Pad | Message | Direction | Pad | Message | Pad | Hash |

|-------|-----|---------|-----------|-----|---------|-----|------|

|       |     | ID      | Bit       |     | Counter |     |      |

## **FIG. 15A**

## **Delete**

| BoxID | GameID | Pad | Message | Direction | Pad | Message | Pad | Hash |

|-------|--------|-----|---------|-----------|-----|---------|-----|------|

|       |        |     | ID      | Bit       |     | Counter |     |      |

## FIG. 15B

## **GamePresentPacket**

| BoxID | GameID | Pad | Message | Direction | Pad | Message | Pad | Hash |

|-------|--------|-----|---------|-----------|-----|---------|-----|------|

|       |        |     | ID      | Bit       |     | Counter |     |      |

FIG. 15C

## **GameIDsPacket**

| Offset | Size | Name                | Size | Name                | Size | Name                  | Description   |

|--------|------|---------------------|------|---------------------|------|-----------------------|---------------|

|        |      | IDcount             |      | Reserved            |      | Reserved              | Total gameIDs |

| •••    |      | GameID <sub>1</sub> |      | Status <sub>1</sub> |      | Reserved <sub>1</sub> | First gameID  |

| •••    |      | ***                 |      |                     |      | •••                   | •••           |

## **FIG. 15D**

## ContextPacket

| GameID | Success=FFh | Size | Size | Size | Fill     | C & R Seed for Browser, |

|--------|-------------|------|------|------|----------|-------------------------|

|        | Fail=00h    | 0    | 1    | 2    | with 00f | otherwise fill with 00f |

## FIG. 15E

## **GRPacket**

| BoxID | Pad | Game | Pad | Message | Direction | Pad | Message | Pad | Hash |

|-------|-----|------|-----|---------|-----------|-----|---------|-----|------|

|       |     | Code |     | ID      | Bit       |     | Counter |     |      |

FIG. 15F

US 6,468,160 B2

## **DLPacket**

| NAME         | DESCRIPTION                                          |

|--------------|------------------------------------------------------|

|              | HEADER                                               |

| gameID       | 0x0001 - 0xFFEF = gameID (Allocated by Manufacturer) |

| PAD          | Random Padding                                       |

| tLengthReq   | Number of Chunks required for application            |

| PAD          | Random Padding                                       |

| Sig          | Hash of Active, protected partitions 0 & 1           |

| PAD          | Random Padding                                       |

| ResetCounter | Reset Both Counts to 0 if ResetCounter = 174         |

| PAD          | Random Padding                                       |

|              | Partition 0 (ENCRYPTED PROGRAM)                      |

| Permissions0 | 0 = ReadOnlyEncrypted, 1 = ReadOnlyClearText         |

| PAD          | Random Padding                                       |

| pLengthReq0  | Number of Chunks reserved in partition               |

| pLengthUsed0 | Number of Chunks active in partition                 |

| PAD          | Random Padding                                       |

|              | Partition 1 (READ ONLY DATA)                         |

| Permissions1 | 1 = ReadOnlyClearText                                |

| PAD          | Random Padding                                       |

| pLengthReq1  | Number of Chunks reserved in partition               |

| pLengthUsed1 | Number of Chunks active in partition                 |

| PAD          | Random Padding                                       |

|              | Partition 2 (READ/WRITE DATA)                        |

| Permissions2 | 2 = Read/Write ClearText                             |

| PAD          | Random Padding                                       |

| pLengthReq2  | Number of Chunks reserved in partition               |

| pLengthUsed2 | Number of Chunks active in partition                 |

| PAD          | Random Padding                                       |

|              | Trailer                                              |

| PAD          | Random Padding                                       |

| BoxID        | BoxID                                                |

| PAD          | Fill with random padding                             |

| MessageID    | Message Counter                                      |

| Direction    | Set to 0                                             |

| Hash         | Davies-Meyer check sum                               |

FIG. 15G

## START DL PACKET

| VALUE          | NAME         | DESCRIPTION                                               |

|----------------|--------------|-----------------------------------------------------------|

|                |              | HEADER                                                    |

| limitedID      | gameID       | 0x8000 - 0xFFEF = gameID Disk (Allocated by Manufacturer) |

| < = 8          | tLengthReq   | Number of Chunks required for application                 |

| gameID         | Sig          | Hash of Active, protected partitions                      |

|                |              | Partition 0 (ENCRYPTED PROGRAM)                           |

| 0              | Permissions0 | 1 = ReadOnlyEncrypted, 2 = ReadOnlyClearText              |

| 0              | pLengthReq0  | Number of Chunks reserved in partition                    |

| 0              | pLengthUsed0 | Number of Chunks active in partition                      |

|                |              | Partition 1 (READ ONLY DATA)                              |

| 1              | Permission1  | 2 = ReadOnlyClearText                                     |

| 0              | pLengthReq1  | Number of Chunks reserved in partition                    |

| 0              | pLengthUsed1 | Number of Chunks active in partition                      |

|                |              | Partition 2 (READ/WRITE DATA)                             |

| 2              | Permissions2 | 3 = Read/Write ClearText                                  |

| tLengthReq     | pLengthReq2  | Number of Chunks reserved in partition                    |

| < = tLengthReq | pLengthUsed2 | Number of Chunks active in partition                      |

|                |              | Trailer                                                   |

| gameID         | BoxID        | BoxID                                                     |

| 0              | MessageID    | Message Counter                                           |

| FFh            | Direction    | Set to 0                                                  |

| Hash           | Hash         | Davies-Meyer Hash                                         |

FIG. 16

| OFFSET | SIZE | NAME            | USAGE      |

|--------|------|-----------------|------------|

|        | •••  | GameID          |            |

|        |      | Status          | (Fig. 18B) |

|        | 111  | Start Chunk 0   |            |

|        | •••  | Length Chunks 0 |            |

Used Chunks 0

Start Chunk 1

Length Chunks 1 Used Chunks 1

Start Chunk 2

Length Chunks 2

Used Chunks 2

Reserved

**FIG. 18A**

| BITS | NAME              | USAGE                                   |

|------|-------------------|-----------------------------------------|

| 0    | Dirty             | Update in process                       |

| 1    | Compact           | Compaction in process on this partition |

| 2    | Used <sub>0</sub> | Indicates that partition 0 is used      |

| 3    | Used <sub>1</sub> | Indicates that partition 1 is used      |

| 4    | Used <sub>2</sub> | Indicates that partition 2 is used      |

| 5    | Reserved          |                                         |

| 6    | Reserved          |                                         |

| 7    | Reserved          |                                         |

**FIG. 18B**

### SECURITY SYSTEM FOR VIDEO GAME SYSTEM WITH HARD DISK DRIVE AND INTERNET ACCESS CAPABILITY

This is a continuation-in-part of U.S. application Ser. No. 5 09/288,293, filed Apr. 8, 1999 entitled "Home Video Game System With Hard Disk Drive and Internet Access Capability", which application is hereby incorporated by reference herein in its entirety.

#### FIELD OF THE INVENTION

The invention generally relates to a security system for a computer system having Internet access capability. More particularly, the invention relates to a security system for a home video game system enhanced to include a modem and hard disk drive which allows a video game player to dial-up a network service provider and communicate over the service provider's network to access the World Wide Web, send e-mail, play games and/or download executable programs, video and audio data to the system's hard disk drive.

### BACKGROUND AND SUMMARY OF THE INVENTION

Over the years, special purpose home video game systems have been (and continue to be) immensely popular, notwithstanding the ever increasing presence of personal computers in households throughout the world. The latest generation of such dedicated video game systems utilize a user's color television to generate exciting game play involving three dimensional game worlds having striking depth and realism involving numerous animated moving objects.

For the virtual millions of game players taking advantage of such low cost, special purpose video game systems, system operation and game play has been characterized by single location, stand alone operation. While home video game systems are designed for more than one player to play using multiple controllers attached to a single video game play console, such dedicated video game systems typically do not permit game play against other remotely located players.

Video game and video game system manufacturers and developers have heretofore faced continual piracy attacks. For the most part, in cartridge-based video game systems, these attacks have come from unscrupulous counterfeiters who produce and sell illegal cartridges. Particularly for cartridge-based video game systems, end user piracy of video games has not been a major problem to combat.

In copending parent application Ser. No. 09/288,293, a system is described which advantageously converts a heretofore stand alone, special purpose video game system into 50 a network communicating device with bulk storage capacity having numerous enhanced capabilities such as simultaneous game play video and Internet display. As used herein, the "Internet" refers to the vast collection of interconnected more generic interconnection of two or more networks.

In accordance with one exemplary embodiment of the incorporated copending application, an expansion device is connected to an existing video game system port to provide additional communication and storage capability via a modem and hard disk drive. A cable TV tuner is also included in the expansion device to assist in advantageously providing a unique picture-in-picture video capability, and data acquisition from the television vertical blanking interval.

With the addition of a modem and hard drive to a home video game system, the piracy issues become dramatically

more serious and complex. For example, the personal computer industry has faced rampant end user piracy and the system described herein and in copending application Ser. No. 09/288,293 is likely to face the same type of pirating

A failure to properly secure such a system, which has been commercialized in part to take advantage of its ability to download purchased games, could be commercially disastrous. If an end user could simply download games from, for 10 example, sellers of pirated games, a significant and perhaps catastrophic revenue stream loss could result from such activity.

The present invention advantageously provides a unique, multilevel security system for use in a computer system having Internet access capability and which precludes, inter alia, downloading and execution of unauthorized programs.

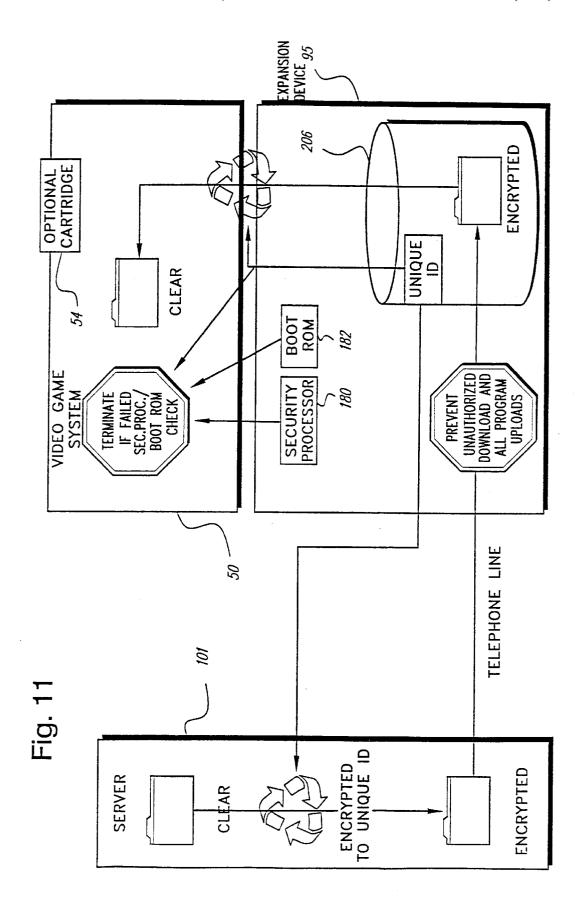

In accordance with one embodiment of the present invention, the primary system security features are incorporated into a video game system expansion device having a hard disk drive. The security system does not rely on the relatively insecure video game system.

The present exemplary embodiment focuses security control in a disk drive/mass media controlling engine which is physically disposed within the expansion device housing as close as possible to the hard disk drive and the downloaded video games and other data it is designed to protect. Security features are incorporated into, for example, a disk drive controlling processing engine to provide security features which extend far beyond simplistic password systems which have heretofore been utilized in conjunction with disk drive controllers.

Security is in part controlled by a server which downloads control information to a digital processor associated with hard drive 206. The disk drive controller processor utilizes this control information to control disk partitions that are created, and to control which applications can have access to respective partitions. The relatively insecure video game system has no control over which partitions may be accessible.

The disk controller processor responds to commands from the server to set up the disk partitioning. Thus, in accordance with one embodiment of the present invention, a direct security link exists between the server and a disk drive 45 controller resident within the expansion device. The server preferably incorporates the highest degree of available Internet security features.

In accordance with an exemplary embodiment of the present invention, each expansion device includes a unique ID associated with its mass media storage device. Unique encryption keys are advantageously for each expansion device to ensure secure communications between the expansion device and the server. Thus, when a request is made through expansion device for downloading, for example, a networks that all use the TCP/IP protocols as well as the 55 particular video game, the server is able to rely on the request coming from an authorized expansion device and not an unauthorized device mimicking the expansion device.

> In accordance with an exemplary embodiment of the present invention, the disk controller also incorporates an encrypting engine which encrypts in accordance with a highly secure encrypting algorithm.

A further level of security is provided in the illustrative embodiments by partitioning the hard drive into various partitions whose security/accessibility is tightly controlled. 65 Each application program, e.g., a video game, has a predetermined number of private partitions, including a read only encrypted partition, where its executable code resides, a read

only data partition for holding less secure data which is not encrypted to permit faster execution since no decryption step is required, and a third partition for storing a wide range of game related data, such as a player's high score, the current location in a game.

The game downloading procedure is controlled at the server so that only authorized games are permitted to be downloaded. Each game is encrypted with an encryption key unique to each individual hard drive. The server utilizes the unique ID and encryption keys for each deck to encrypt downloaded game software. The server has a list of at least three items for each game, including the unique expansion device ID, e.g., serial number, an expansion device box encryption key, used for communications between the server and the expansion device, and a game encryption key which 15 is utilized by the server to encrypt games for the expansion device 95. In playing a game, the server identifies to a disk controller in an expansion device 95, the disk partitions to which that particular game may have access. In accordance with the illustrative embodiments, the game program is 20 decrypted by the disk controller encrypting engine before it may be played.

The above-described features and other advantages of the present invention will become apparent from the following detailed description of the present invention when taken in conjunction with the accompanying drawings.

### BRIEF DESCRIPTION OF THE DRAWINGS

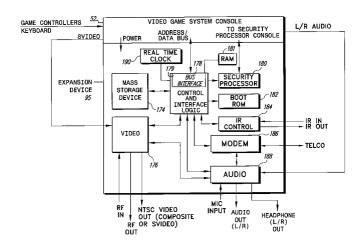

FIG. 1A is a perspective illustration of an exemplary embodiment of the present invention.

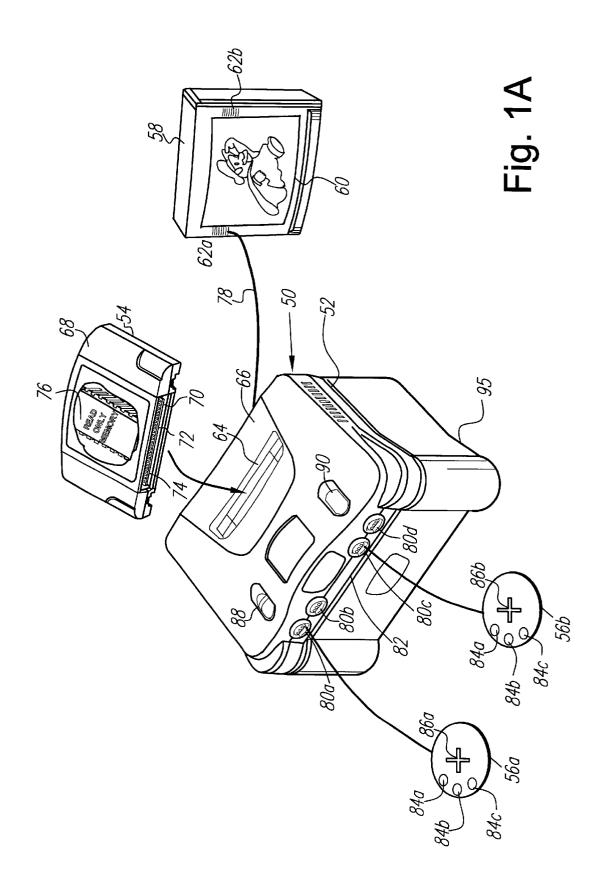

FIG. 1B is a block diagram of part of FIG. 1A.

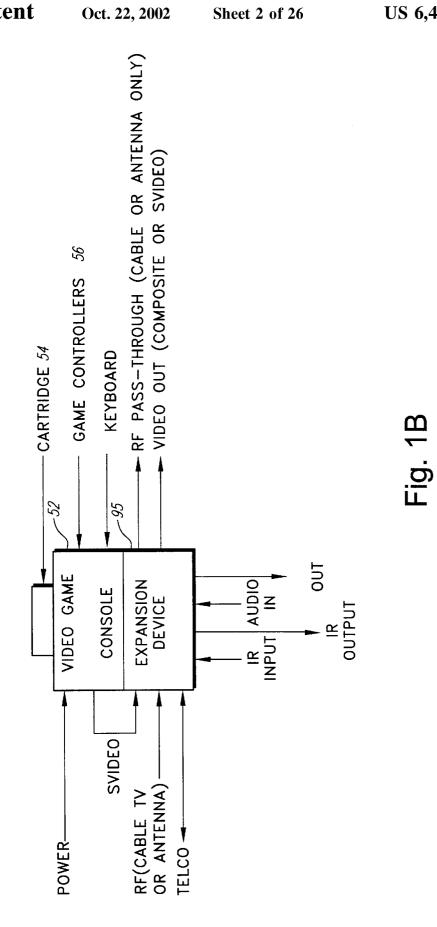

FIG. 1C is an illustrative component interconnection diagram showing an exemplary embodiment of the present invention in a home video game system context.

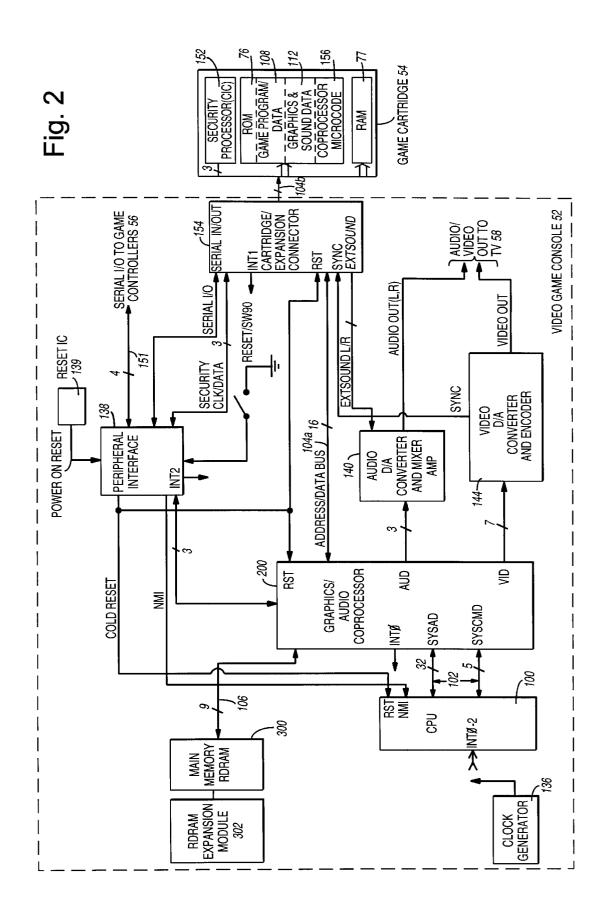

FIG. 2 is a block diagram of an exemplary embodiment of a video game console coupled to a game cartridge.

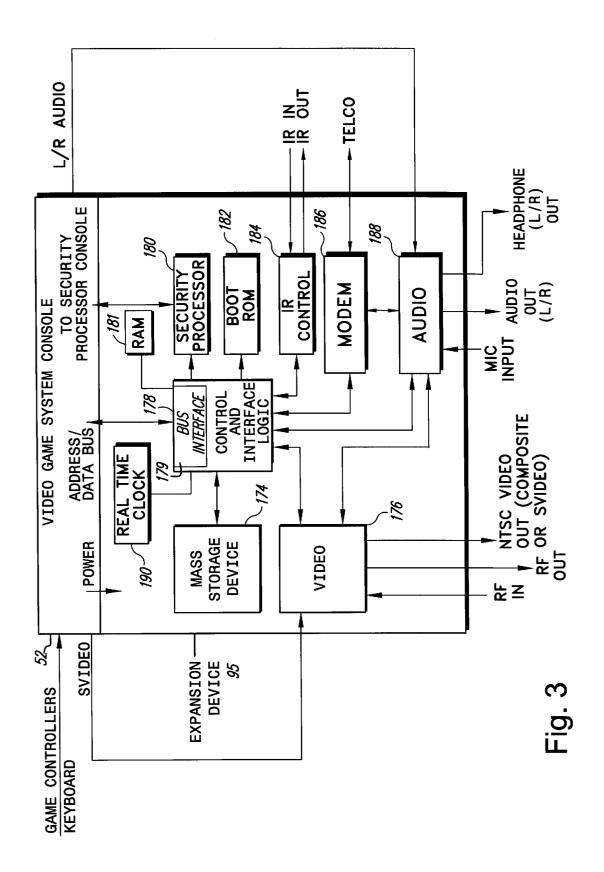

FIG. 3 is a block diagram of the system shown in FIGS. 1A and 1B showing the expansion device in further detail.

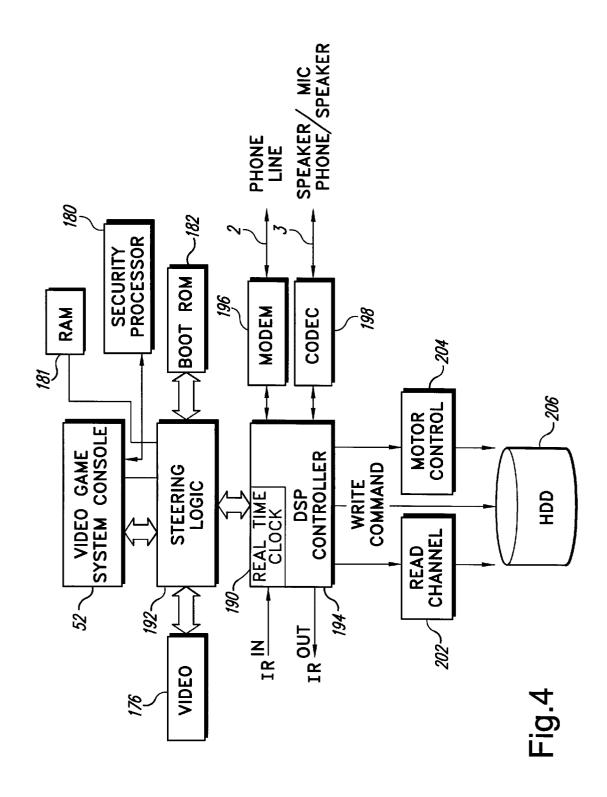

FIG. 4 is a more detailed block diagram of the expansion 40 device shown in FIG. 3 depicting a preferred integrated modem and mass storage device control.

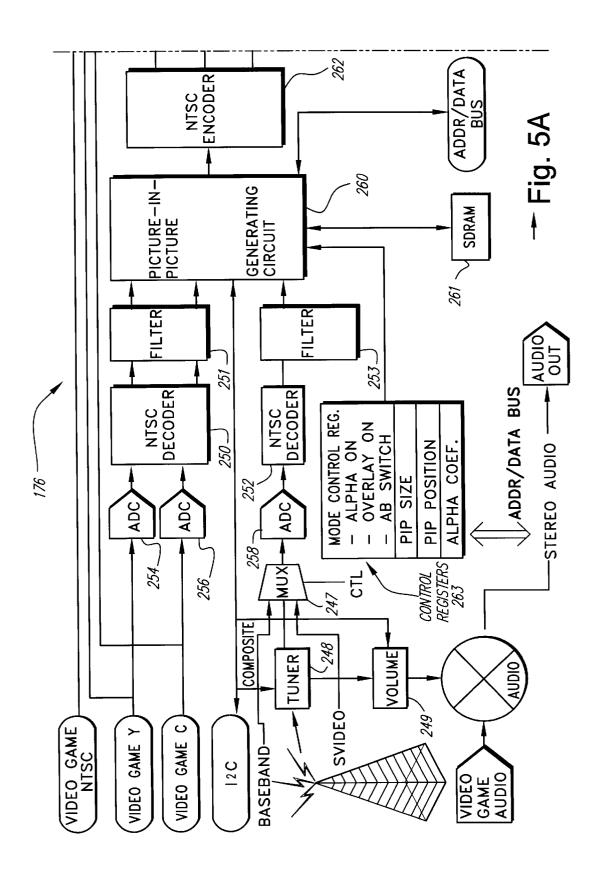

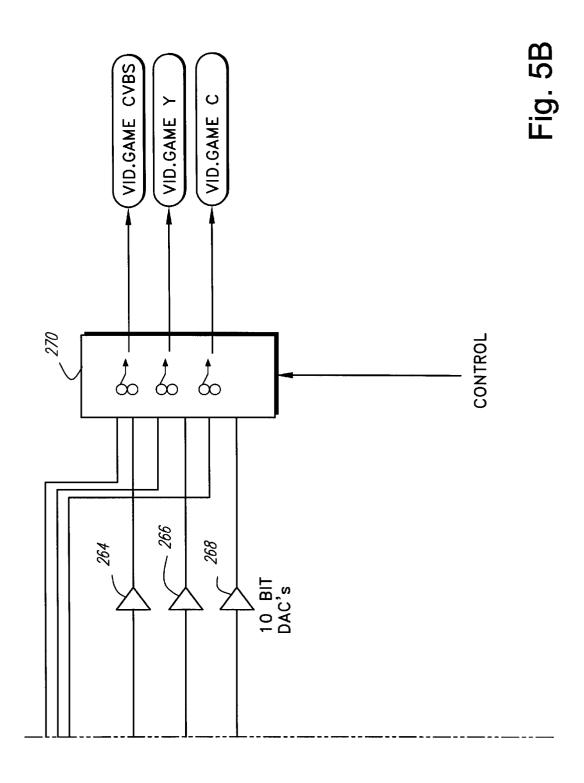

FIGS. 5A and 5B are a block diagram of the video circuit shown in FIGS. 3 and 4.

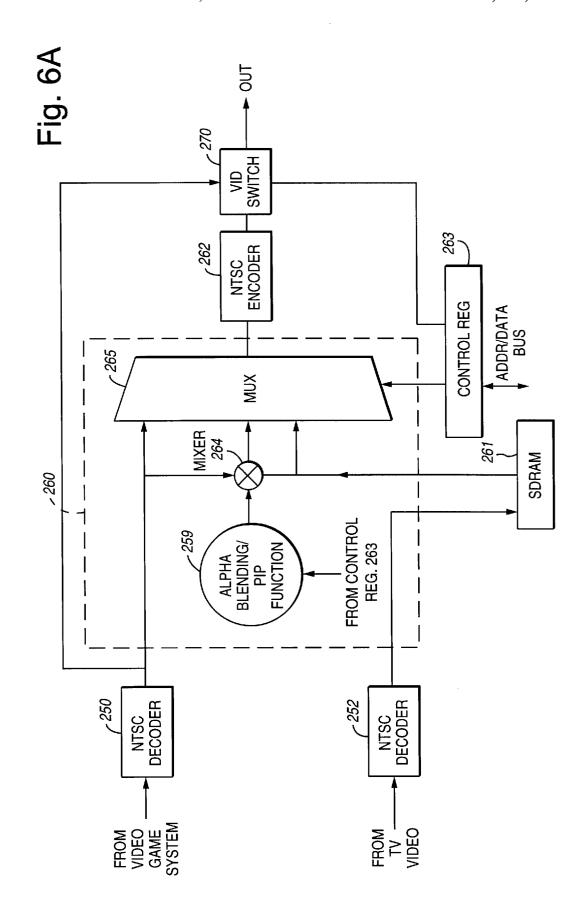

FIG. **6A** is a block diagram depicting an exemplary <sup>45</sup> picture-in-picture generating circuit in further detail in conjunction with other components shown in FIG. **5A** and FIG. **5B**.

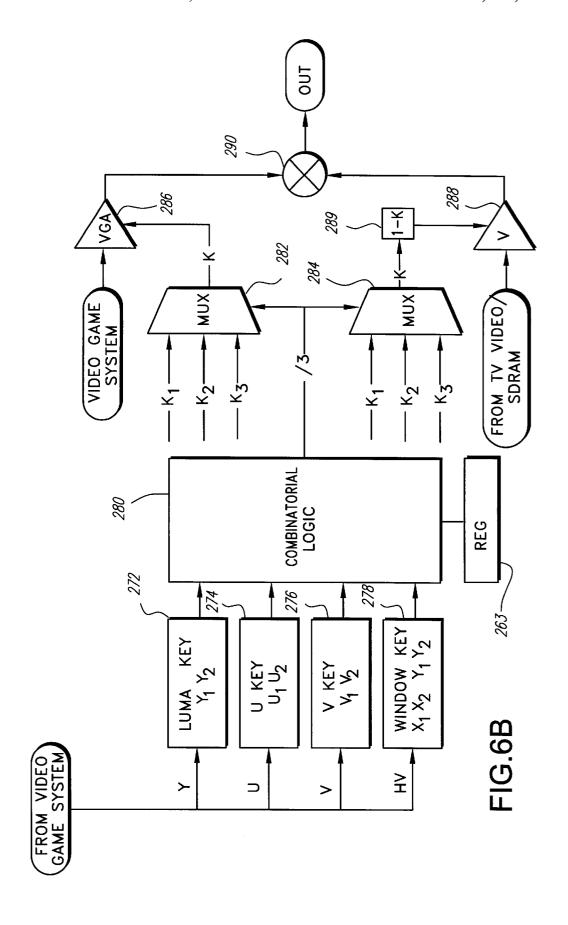

FIG. 6B shows an exemplary implementation of picture-in-picture generating circuit 260 shown in FIG. 6A.

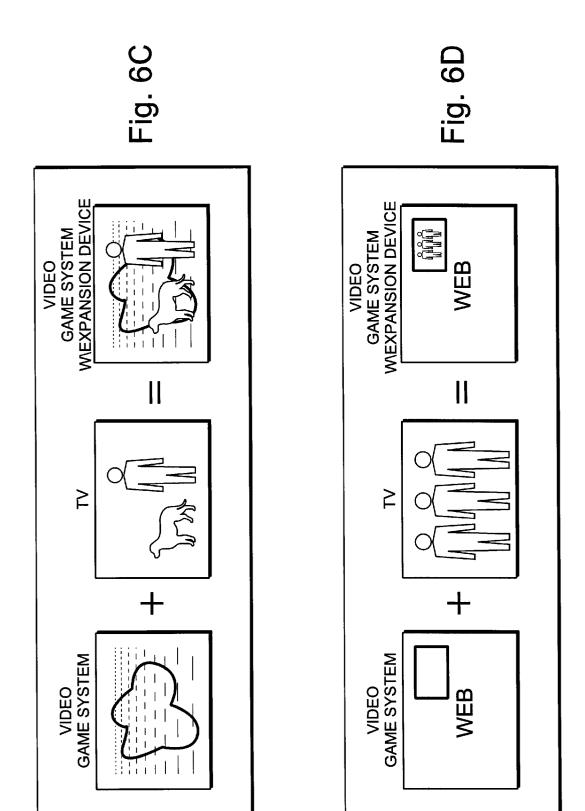

FIGS. 6C and 6D show exemplary overlay screen displays which may be generated in accordance with the present invention.

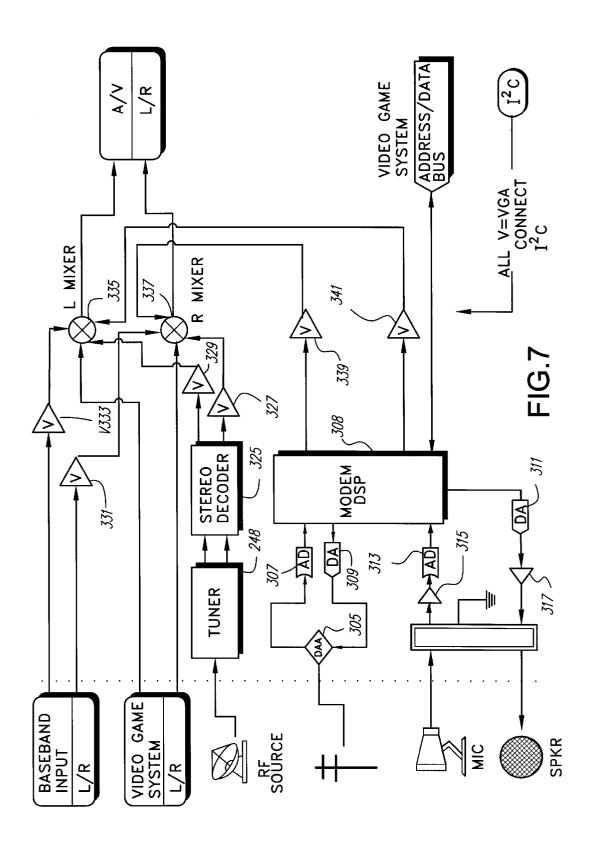

FIG. 7 depicts the audio/modem processing circuit in further detail.

FIG. 8 is an exemplary video game system memory map.

FIG. 9 shows exemplary contents of an interrupt status register.

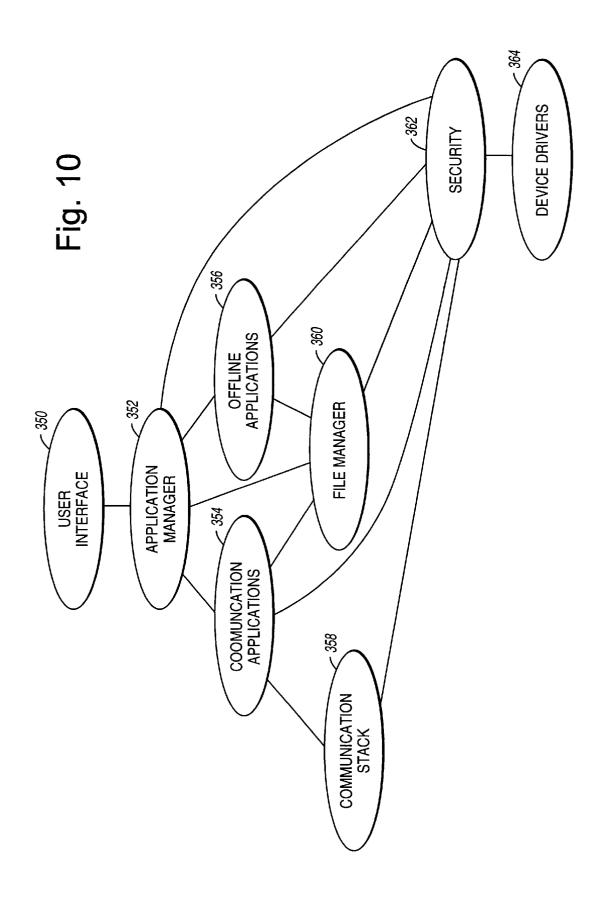

FIG. 10 is a block diagram of system software modules in  $_{60}$  accordance with the present exemplary embodiment.

FIG. 11 is an exemplary block/flow diagram of security features which may be utilized in the illustrative embodiments.

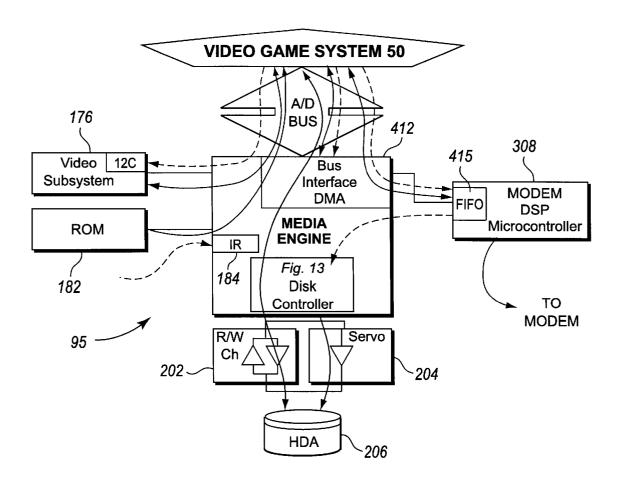

FIG. 12 is an illustrative block diagram showing the data 65 and control signal flow between the video game system and the media engine.

4

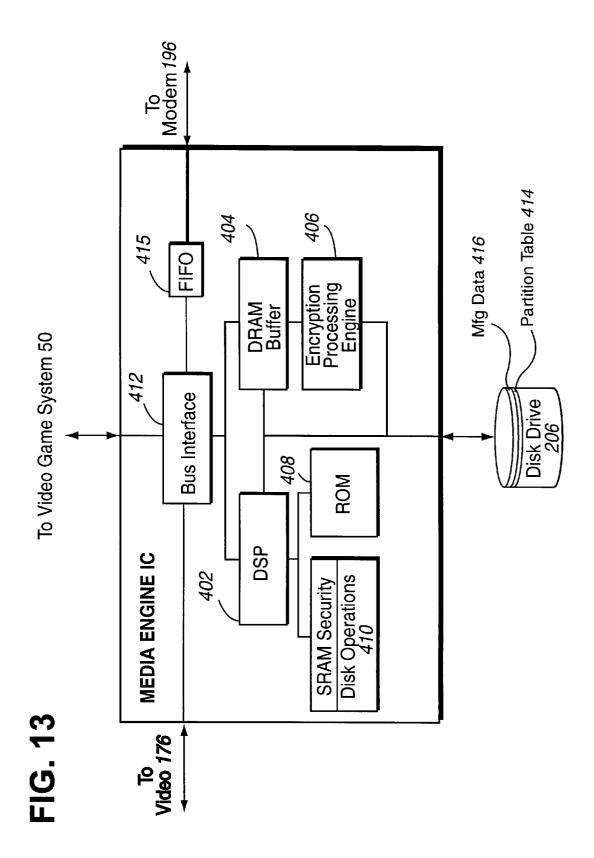

FIG. 13 is a more detailed block diagram of the media engine hardware components.

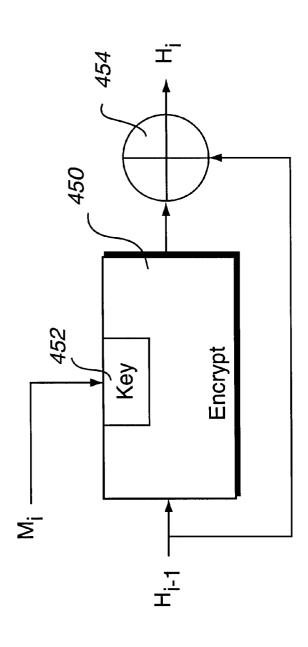

FIG. 14 is a block diagram for explaining the operation of an exemplary hashing algorithm.

FIGS. 15A through 15G are exemplary data packets used in the security system described in the illustrative embodiments.

FIG. 16 is an exemplary start download packet used during the download process.

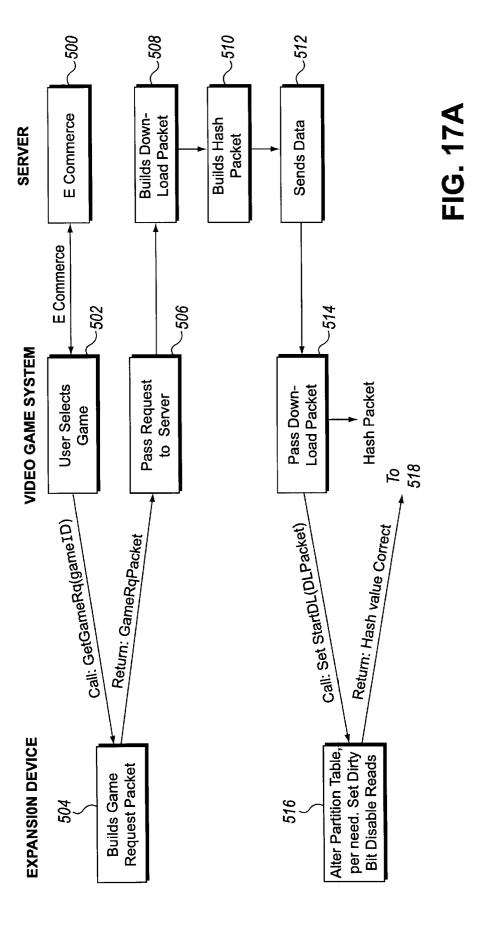

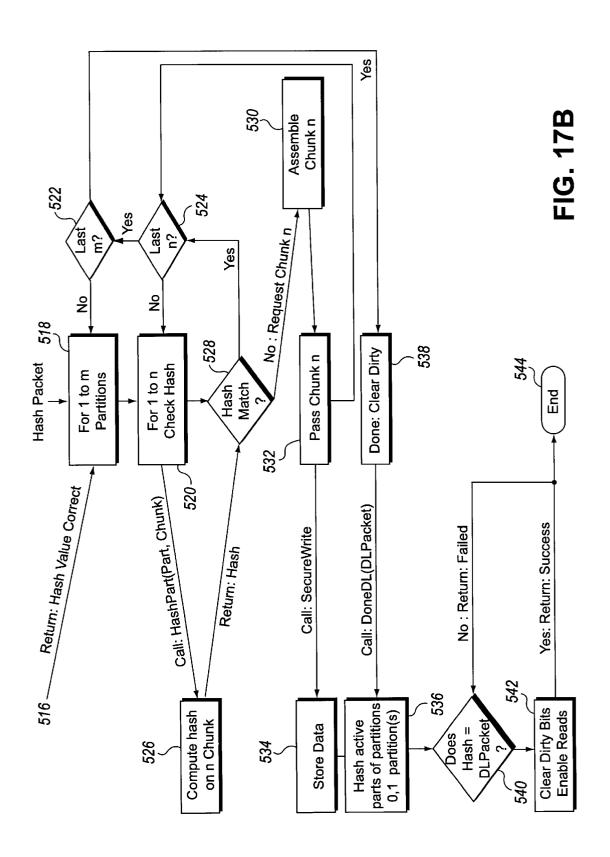

FIGS. 17A and 17B are a flowchart depicting an illustrative download process.

FIG. 18A is an illustration of an exemplary partition table stored in disk drive.

FIG. 18b is an associated partition table status bit table.

## DETAILED DESCRIPTION OF THE PRESENT PREFERRED EMBODIMENT

Prior to explaining the details of an exemplary embodiment of the security system of the present invention, an illustrative video game system with which the exemplary security system is designed to operate will first be explained in conjunction with FIGS. 1 through 10. The security features in accordance with various illustrative embodiments will then be explained in detail in conjunction with FIGS. 11 through 17.

FIG. 1A is a perspective view of a presently preferred embodiment of the present invention showing an exemplary video game system 50 connected to a communications and bulk media expansion device 95. In the present exemplary embodiment, the video game system 50 may, for example, be the commercially available Nintendo 64 Video Game System. It should be recognized that the present invention is not limited to use with this exemplary video game system but rather may be adapted for use with a wide range of existing video game systems. Additionally, although the present invention is illustratively described using an add-on expansion device, it is contemplated that the enhanced video game system described herein may alternatively be packaged in a common integrated housing and sold as a single unit

In accordance with one embodiment of the present invention, expansion device 95 is connected to an expansion port (not shown) located, for example, on the bottom housing portion of video game system 50. Even with the expansion device 95 attached to the video game 50, if a game cartridge 54 is inserted into the console 52, the system will start under control of the program resident in cartridge 54.

Otherwise, it will start under control of a program resident on the hard disk drive embodied in expansion device 95 as described below.

Expansion device 95, as shown in FIG. 1A, is preferably mechanically configured to match the appearance of the video game system console 52 and includes a modem and hard disk drive, as well as many other features described in detail below. In accordance with an exemplary embodiment, expansion device 95 allows a video game player to dial up a network service provider and communicate over the service provider's network to access and surf the World Wide Web, send and receive e-mail, send real time messages and chat, play games and/or download video and/or audio information to the expansion device 95's hard disk drive. The expansion device 95 supports disk-based game play with both program and game data storage. The hard disk drive preferably has a capacity of at least one gigabyte. The modem associated with expansion device 95 should prefer-

ably be at least V.34 (33.6 baud) in performance and support caller ID, full duplex speaker phone and answering machine functions. Communication expansion device 95 is designed to be connected to external peripherals such as printers and video components and includes a cable TV tuner and video circuitry having picture-in-picture video capability and video overlay capability providing the ability to mix television video and video generated during video game play.

As shown in FIG. 1A, video game system 50 includes a main console 52, a video game storage device 54, and handheld controllers 56a,b (or other user input devices). Main console 52 is connected to a conventional home color television set 58. Television set 58 displays 3D video game images on its television screen 60 and reproduces stereo sound through its speakers 62a,b.

In the illustrative embodiment, the video game storage device 54 is in the form of a replaceable memory cartridge insertable into a slot 64 on a top surface 66 of console 52. A wide variety of alternative program storage media are contemplated by the present invention such as CD ROM, floppy disk, etc. In this exemplary embodiment, video game  $\ ^{20}$ storage device 54 comprises a plastic housing 68 encasing a printed circuit board 70. Printed circuit board 70 has an edge 72 defining a number of electrical contacts 74. When the video game storage device 68 is inserted into main console slot 64, the cartridge electrical contacts 74 mate with corresponding "edge connector" electrical contacts within the main console This action electrically connects the storage device printed circuit board 72 to the electronics within main console 52. In this example, at least a "read only memory" chip 76 is disposed on printed circuit board 70 within storage device housing 68. This "read only memory" chip 76 stores instructions and other information pertaining to a particular video game. The read only memory chip 76 for one game cartridge storage device 54 may, for example, contain instructions and other information for an adventure game while another storage device 54 may contain instructions and information to play a car race game, an educational game, etc. If the system is being operated using a game cartridge as opposed to via the expansion device 95, to play one game as opposed to another game, the user of video game system 50 need only plug the appropriate storage device 54 into main console slot 64—thereby connecting the storage device's read only memory chip 76 (and any other circuitry it may contain) to console 52. This enables a computer system embodied within console 52 to access the information contained within read only memory 76, which 45 information controls the console computer system to play the appropriate video game by displaying images and reproducing sound on color television set 58 as specified under control of the read only memory game program information.

up the video game system 50 for game play, the user first connects console 52 to color television set 58 by hooking a cable 78 between the two. Console 52 produces both "video" signals and "audio" signals for controlling color television the television screen 60 and the "audio" signals are played back as sound through television loudspeaker 62. Depending on the type of color television set 58, it may be necessary to connect a conventional "RF modulator" between console 52 and color television set 58. This "RF modulator" (not shown) converts the direct video and audio outputs of console 52 into a broadcast type television signal (e.g., for a television channel 2 or 3) that can be received and processed using the television set's internal "tuner." Other conventional color television sets 58 have direct video and 65 audio input jacks and therefore don't need this intermediary RF modulator.

The user then needs to connect console 52 to a power

This power source may comprise a conventional AC adapter (not shown) that plugs into a standard home electrical wall socket and converts the house voltage into a lower voltage DC signal suitable for powering console 52. The user may then connect up to 4 hand controllers 56a, 56b to corresponding connectors 80a-80d on main unit front panel 82.

Controllers 56 may take a variety of forms and the controller depicted in FIG. 1A is only for illustrative purposes only. In this example, the controllers 56a,b include various function controlling push buttons such as 84a-c and X-Y switches **86***a*,*b* used, for example, to specify the direction (up, down, left or right) that a player controllable character displayed on television screen 60 should move. Other controller possibilities include joysticks, mice pointer controls, a keyboard, and a wide range of other conventional user input devices. The presently preferred controller for use in system 50 is disclosed in FIGS. 6 through 7 of the applicants'assignee's copending application Ser. No. 08/719,019, entitled "Operation Controlling Device and Video Processing System Used Therewith", which application is incorporated herein by reference in its entirety.

The video game system 50 is designed to accommodate expansion to incorporate various types of peripheral devices yet to be specified. This is accomplished by incorporating a programmable peripheral device input/output system which permits device type and status to be specified by program commands.

In the cartridge based mode of operation, a user selects a storage device 54 containing a desired video game, and inserts that storage device into console slot 64 (thereby electrically connecting read only memory 76 and other cartridge electronics to the main console electronics). The user then operates a power switch 88 to turn on the video game system 50 and operates controllers 86a,b (depending on the particular video game being played, up to four controllers for four different players can be used with the illustrative console) to provide inputs to console 52 and thus control video game play. For example, depressing one of push buttons 84a-c may cause the game to start playing. Moving directional switch 86 may cause animated characters to move on the television screen 60 in controllably different directions. Depending upon the particular video game stored within the storage device 54, these various controls 84, 86 on the controller 56 can perform different functions at different times. If the user wants to restart game In accordance with one exemplary implementation, to set 50 play from the beginning, or alternatively with certain game programs reset the game to a known continuation point, the user can press a reset button 90.

FIG. 1B schematically shows the input and output signals associated with video game console 52 and expansion set 58. The "video" signals control the images displayed on 55 device 95. Expansion device 95 is coupled to a video console 52 expansion connector, which preferably is the mirror image of the cartridge connector bus such as exemplary embodiment cartridge connector 154 shown in FIG. 2. As is described further below, expansion device 95 includes a hard drive, a video section with a TV tuner, and a modem.

> Expansion device 95 receives the highest quality video output signal from video game console 52 (SVIDEO). In the alternative embodiment, where the expansion device and video game system are combined as an integrated unit, the signal from the video game system would be a digital RGB signal instead of an SVIDEO signal TV signals are coupled to the expansion device 95 via the RF input from either cable

TV or off-air signals or via baseband. These RF or baseband signals are blended with the output signals from the video game console **52**. In this fashion, a user may watch TV while viewing overlay information from the video game console. RF data may be delivered via the RF input and captured during the video vertical blanking interval if desired.

Video game console 52, as shown in FIGS. 1A, 1B, and 2, is coupled to game controllers 56. In accordance with one embodiment of the present invention, Internet operations may be controlled via a game controller 56 as shown in the 10 is a Direct Broadcast Satellite box. above-identified application Ser. No. 08/719,019. However, a preferred Internet access input device is a keyboard which permits convenient text entry operations. A wired keyboard may, for example, be coupled to one of the controller ports 80A-80D shown in FIG. 1A and will preferably interface with the same control logic as a game controller 86. Alternatively, a wireless infrared keyboard or the like could be used as a text entry device.

The expansion device 95 includes a RF pass-through output which operates to pass the TV signal from expansion device 95 to, for example, a user's TV or VCR. Expansion device 95 also includes a video output which feeds either a composite video output signal or SVIDEO output signal and includes an input/output connection to the telephone system which is coupled to a modern within expansion device 95.

As shown in FIG. 1B, expansion device 95 includes an audio input which permits, for example, interconnection with a microphone. The microphone permits taking advantage of the DSVD capabilities of the expansion device modem. In this context, the modem mixes data coming from the video game console 52 and input audio information. The microphone may be used for voice input which may be digitized for use in a game. The audio input also permits the input of other audio information which may then be digitized and coupled to video game console 52 for use in a game. Alternatively, the input audio information may be directly coupled to an associated speaker. Expansion device 95 also includes an audio output that may be directly coupled to the user's TV and/or a headset.

Expansion device 95 also includes infrared IR control. Infrared input signal processing, for example, permits a TV tuner within expansion device 95 to be remotely controlled via the IR input signal. The IR controller may be linked to the TV tuner after IR information is processed in the video game console 52, or alternatively the information may be processed by an IR control CPU in expansion device 95. The IR output is used to control an associated cable box that may be coupled to the RF input described above. Thus the IR output may be used to change channels via an associated cable box. The IR output may, for example, be used to remotely control the TV power or to control recording in an associated VCR. The television power may be controlled, for example, by a user depressing the "Power" button on a hand-held IR remote. The IR signal is sent to the expansion 55 device 95 IR input.

The expansion device 95 sends this information to the video game console 52. The video game console 52 recognizes this as a "Power" button depression. It then commands the expansion device 95 to output the IR signal to the TV that commands the TV to toggle its power. The overall system is powered via a power input from game console 52.

In accordance with another exemplary embodiment, the IR output may control both a cable box and a VCR at the same time. For example, two IR LEDs may be placed on a 65 single output. One IR LED could be placed next to the VCR, the other next to the cable box. The signal generated by the

expansion device 95 causes both LEDs to flash at the same time with the same signal. The cable box sees transmissions intended for the VCR, and the VCR sees transmissions intended for the cable box, but since each device is programmed to respond only to its own unique set of signals, one device will ignore the signals intended for the other device. In this way, two devices may be controlled with the same signal output.

Another device which may be controlled by the IR output

The system shown in FIG. 1B permits a user to receive enhanced television services. For example, a TV channel guide may be downloaded via the Internet, allowing a user to spot a desired program and to immediately tune to the program via the expansion device TV tuner and IR input. The IR signal may be coupled to the cable box, a Direct Broadcast Satellite Box, or a VCR. The TV channel guide may be captured from data transmitted in the vertical blanking interval of a television signal. In one exemplary embodiment, the signal from a remote controller is not directly linked to the IR transmitter. The video game console 52 first interprets the IR signal, then remaps the signal to the device to be controlled via the IR transmitter.

The system shown in FIG. 1B also permits a user to watch TV while simultaneously logging onto the Internet. This feature advantageously allows a user to observe his or her favorite news, sports or entertainment show while waiting for Internet access. Expansion device 95 permits the video game console 52 to be coupled to the Internet to play multiplayer games, or alternatively, to dial a friend and play a game involving head-to-head competition.

Expansion device 95 also provides video game console 52 with a mass storage device (such as a hard drive) to permit the downloading of entire games onto the mass storage device. The purpose of the mass storage device is not only for downloading entire games, but also for caching of internet data to permit user-friendly viewing of internet pages. It is also for storing downloaded upgrades of games, additional levels of games, and non-game data such as text files.

If the system is used with a game cartridge 54, game cartridge 54 may be programmed to utilize the expansion device modem and mass storage device. Alternatively, in one embodiment of the present invention, the system shown in FIG. 1B may be operated without a cartridge 54.

FIG. 1C is an illustrative component interconnection diagram showing an exemplary embodiment of the present invention in a home video game system context. As shown in FIG. 1C, a television signal is transmitted to a cable TV box 57, which outputs, for example, a broadband output signal that is coupled to the RF input of expansion device 95. The cable TV box 57 may alternatively be a Direct Satellite Broadcast box, or a broadcast TV antenna. Expansion device 95 is also coupled to video game system console 52 as shown in FIGS. 1A and 1B.

The input broadband TV signal is split by distributor 59 such that the RF signal is in one path input to tuner 248 and in another path is passed through to bypass switch 63. Tuner 248 provides a demodulated baseband signal, which is coupled to the video subsystem 176. The video subsystem output is modulated by RF modulator 61 to a broadband signal, and the broadband signal is coupled to bypass switch 63.

Bypass switch 63 is normally in a closed position to provide a bypass path for the input RF signal. Bypass switch 63 provides a bypass path during power down conditions or otherwise switches is response to a switching control signal. Bypass switch 63 is switched to the open position in response to a control signal (for example, received via the I<sup>2</sup>C bus described below in conjunction with FIG. 5A) under program control. Thus, when the system powers down, or in a default condition, an RF output is always coupled to the expansion device 95 output. Alternatively, the bypass switch 63 may be controlled to output signals generated by the video subsystem 176, such as, for example, a picture-in-picture display as will be described in detail below via the 10 audio/video output of expansion device 95.

As shown in FIG. 1C, the baseband video subsystem 176 output and the RF output signal are coupled to respective inputs of the VCR 163. The RF and/or baseband outputs of VCR 63 are coupled to a user's home television 58. As described above in conjunction with FIG. 1B, expansion device 95 also outputs an IR output signal.

Prior to describing further details of expansion device 95, the video game system 50 will be described in conjunction with FIG. 2, which is a block diagram of an illustrative embodiment of console 52 coupled to a game cartridge 54. FIG. 2 shows a main processor 100, a coprocessor 200, and main memory 300 which may include an RDRAM expansion module 302. For a more complete description of the video game system shown in FIG. 2, including details of the peripheral interface 138 and other components, reference is made to the applicants' assignee's copending application Ser. No. 08/562,288, entitled "High Performance/Low Cost, Video Game System With Multifunctional Peripheral Processing Subsystem", which application is incorporated herein by reference in its entirety.

Main processor 100 is the computer that executes the video game program within storage device 54 in conjunction with coprocessor 200. In this example, the main processor 100 accesses this video game program through the coprocessor 200 over a communication path 102 between the main processor and the coprocessor 200, and over another communication path 104a,b between the coprocessor and the video game storage device 54. Alternatively, the main processor 100 can control the coprocessor 200 to copy the video game program from the video game storage device 54 into main memory 300 over path 106, and the main processor 100 can then access the video game program in main memory 300 via coprocessor 200 and paths 102, 106. Main processor 100 accepts inputs from game controllers 56 during the execution of the video game program.

Main processor 100 generates, from time to time, lists of instructions for the coprocessor 200 to perform. Coprocessor 200 may be any compatible coprocessor which supports rapid processing of 3D graphics and digital audio or it may be a special purpose high performance, application specific integrated circuit having an internal design that is optimized for rapidly processing 3D graphics and digital audio information. In response to instruction lists provided by main processor 100 over path 102, coprocessor 200 generates video and audio outputs for application to color television set 58 based on data stored within main memory 300 and/or video game storage device 54.

FIG. 2 also shows that the audio video outputs of coprocessor 200 are not provided directly to television set 58 in this example, but are instead further processed by external electronics outside of the coprocessor. In particular, in this example, coprocessor 200 outputs its audio and video information in digital form, but conventional home color television sets 58 require analog audio and video signals. Therefore, the digital outputs of coprocessor 200 must be

converted into analog form—a function performed for the audio information by DAC and mixer amp 40 and for the video information by VDAC and encoder 144. The analog audio signals generated in DAC 140 are amplified and filtered by an audio amplifier therein that may also mix audio signals generated externally of console 52 via the EXT-SOUND L/R signal from connector 154. The analog video signals generated in VDAC 144 are provided to a video encoder therein which may, for example, convert "RGB" inputs to composite video outputs compatible with commercial TV sets. The amplified stereo audio output of the amplifier in ADAC and mixer amp 140 and the composite video output of video DAC and encoder 144 are provided to directly control home color television set 58. The composite synchronization signal generated by the video digital to analog converter in component 144 is coupled to its video encoder and to external connector 154 for use, for example, by an optional light pen or photogun.

FIG. 2 also shows a clock generator 136 that produces timing signals to time and synchronize the other console 52 components. Different console components require different clocking frequencies, and clock generator 136 provides suitable such clock frequency outputs (or frequencies from which suitable clock frequencies can be derived such as by dividing).

In this illustrative embodiment, game controllers 56 are not connected directly to main processor 100, but instead are connected to console 52 through serial peripheral interface 138. Serial peripheral interface 138 demultiplexes serial data signals incoming from up to four or five game controllers 56 (e.g., 4 controllers from serial I/O bus 151 and 1 controller from connector 154) and provides this data in a predetermined format to main processor 100 via coprocessor 200. Serial peripheral interface 138 is bidirectional, i.e., it is 35 capable of transmitting serial information specified by main processor 100 out of front panel connectors 80a-d in addition to receiving serial information from those front panel connectors. The serial interface 138 receives main memory RDRAM data, clock signals, commands and sends data/ responses via a coprocessor serial interface (not shown). I/O commands are transmitted to the serial interlace 138 for execution by its internal processor as is described in copending application Ser. No. 08/562,288. In this fashion, the peripheral interface's processor by handling I/O tasks, 45 reduces the processing burden on main processor 100. As is described in more detail in application Ser. No. 08/562,288, serial peripheral interface 138 also includes a "boot ROM (read only memory)" that stores a small amount of initial program load (IPL) code. This IPL code stored within the peripheral interface boot ROM is executed by main processor 100 at time of startup and/or reset to allow the main processor to begin executing game program instructions 108 within storage device 54. The initial game program instructions 108 may, in turn, control main processor 100 to initialize the drivers and controllers it needs to access main memory 300.

In this exemplary embodiment when operating in the cartridge game play mode, serial peripheral interface 138 includes a processor (not shown) which, in addition to performing the I/O tasks referred to above, also communicates with an associated security processor 152 within storage device 54 and performs security tasks. This pair of security processors (one in the storage device 54, the other in the console 52) performs, in cooperation with main processor 100, an authentication function to ensure that only authorized storage devices may be used with video game console 52.

As shown in FIG. 2, peripheral interface 138 receives a power-on reset signal from reset IC 139. Reset IC 139 detects an appropriate threshold voltage level and thereafter generates a power-on reset signal which, in turn, results in a cold reset signal being generated, which signal is coupled to the reset input of main processor 100.

FIG. 2 also shows a connector 154 within video game console 52. In this illustrative embodiment, connector 154 connects, in use, to the electrical contacts 74 at the edge 72 of storage device printed circuit board 70. Thus, connector 154 electrically connects coprocessor 200 to storage device ROM 76. Additionally, connector 154 connects the storage device security processor 152 to main unit serial peripheral interface 138. Although connector 154 in the particular example shown in FIG. 2 may be used primarily to read data and instructions from a non-writable read only memory 76, system 52 is designed so that the connector is bidirectional, i.e., the main unit can send information to the storage device 54 for storage in random access memory 77 in addition to reading information from it.

Main memory 300 stores the video game program in the form of CPU instructions 108. All accesses to main memory 300 are through coprocessor 200 over path 106. These CPU instructions are typically copied from the game program/ data 108 stored in storage device 54 and downloaded to RDRAM 300. This architecture is likewise readily adaptable for use with CD ROM or other bulk media devices. Although CPU 100 is capable of executing instructions directly out of storage device ROM 76, the amount of time required to access each instruction from the ROM is much greater than the time required to access instructions from main memory 300. Therefore, main processor 100 typically copies the game program/data 108 from ROM 76 into main memory 300 on an as-needed basis in blocks, and accesses the main memory 300 in order to actually execute the instructions. Memory RD RAM 300 is preferably a fast access dynamic RAM capable of achieving 500 Mbytes/ second access times such as the DRAM sold by RAMBUS, Inc. The memory 300 is coupled to coprocessor 200 via a unified nine bit wide bus 106, the control of which is arbitrated by coprocessor 200. The memory 300 is expandable by merely plugging, for example, an 8 Mbyte memory card into console 52 via a console memory expansion port

The main processor 100 preferably includes an internal 45 cache memory (not shown) used to further decrease instruction access time. Storage device 54 also stores a database of graphics and sound data 112 needed to provide the graphics and sound of the particular video game. Main processor 100, in general, reads the graphics and sound data 112 from 50 storage device 54 on an as-needed basis and stores it into main memory 300 in the form of texture data, sound data and graphics data. In this example, coprocessor 200 includes a display processor having an internal texture memory into which texture data is copied on an as-needed basis for use by 55 the display processor.

Storage device 54 also stores coprocessor microcode 156. In this example, a signal processor within coprocessor 200 executes a computer program in order to perform its various graphics and audio functions. This computer program, called the "microcode," is provided by storage device 54. Typically, main processor 100 copies the microcode 156 into main memory 300 at the time of system startup, and then controls the signal processor to copy parts of the microcode on an as-needed basis into an instruction memory within signal processor for execution. Because the microcode 156 is provided by storage device 54, different storage devices

12

can provide different microcodes—thereby tailoring the particular functions provided by coprocessor 200 under software control. Because the microcode 156 is typically too large to fit into the signal processor's internal instruction memory all at once, different microcode pages or portions may need to be loaded from main memory 300 into the signal processor's instruction memory as needed. For example, one part of the microcode 156 may be loaded into signal processor 400 for graphics processing, and another part of microcode may be loaded for audio processing.

Although not shown in FIG. 2, coprocessor 200 also includes a CPU interface, a serial interface, a parallel peripheral interface, an audio interface, a video interface, a main memory DRAM controller/interface, a main internal bus and timing control circuitry. The coprocessor main bus allows each of the various main components within coprocessor 200 to communicate with one another. The CPU interface is the gateway between main processor 100 and coprocessor 200. Main processor 100 reads data to and writes data from coprocessor CPU interface via a CPU-to-coprocessor bus. A coprocessor serial interface provides an interface between the serial peripheral interface 138 and coprocessor 200, while coprocessor parallel peripheral interface 206 interfaces with the storage device 54 or other parallel devices connected to connector 154.

A coprocessor audio interface reads information from an audio buffer within main memory 300 and outputs it to audio DAC 140. Similarly, a coprocessor video interface reads information from an RDRAM frame buffer and then outputs it to video DAC 144. A coprocessor DRAM controller/interface is the gateway through which coprocessor 200 accesses main memory 300. The coprocessor timing circuitry receives clocking signals from clock generator 136 and distributes them (after appropriate dividing as necessary) to various other circuits within coprocessor 200.

Main processor 100 in this example is a MIPS R4300 RISC microprocessor designed by MIPS Technologies, Inc., Mountain View, Calif. For more information on main processor 100, see, for example, Heinrich, MIPS Microprocessor R4000 User's Manual (MIPS Technologies, Inc., 1984, Second Ed.). The conventional R4300 main processor 100 supports six hardware interrupts, one internal (timer) interrupt, two software interrupts, and one non-maskable interrupt (NMI). In this example, three of the six hardware interrupt inputs (INTO, INT1 and INT2) and the nonmaskable interrupt (NMI) input allow other portions of system 50 to interrupt the main processor. Specifically, main processor INTO is connected to allow coprocessor 200 to interrupt the main processor, the main processor interrupt INT1 is connected to allow storage device 54 or other external devices to interrupt the main processor, and main processor interrupts INT2 and NMI are connected to allow the serial peripheral interface 138 to interrupt the main processor. Any time the processor is interrupted, it looks at an internal interrupt register to determine the cause of the interrupt and then may respond in an appropriate manner (e.g., to read a status register or perform other appropriate action). All but the NMI interrupt input from serial peripheral interface 138 are maskable (i.e., the main processor 100 can selectively enable and disable them under software control).

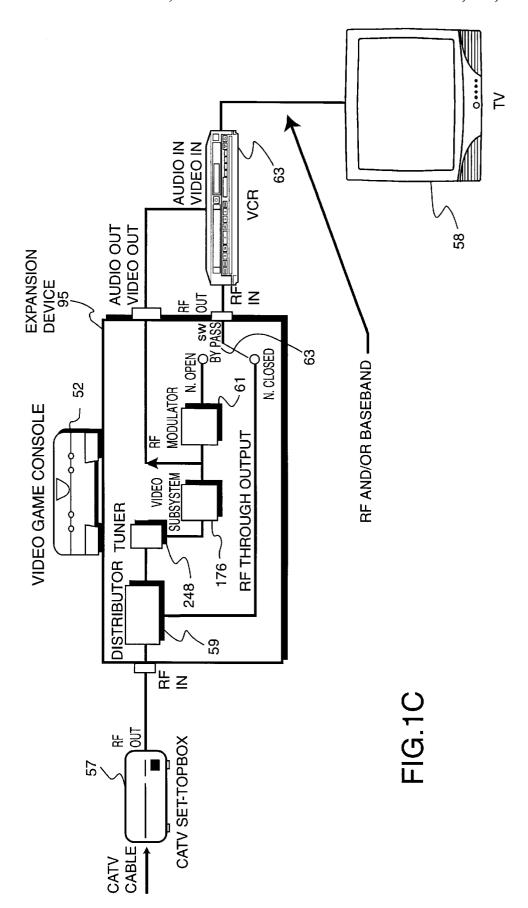

FIG. 3 is a block diagram similar to FIG. 1B but shows the expansion device 95 in further detail. Data and control signals are coupled from video game console 52's address and data (address/data) bus to the expansion device 95 and from expansion device 95 to video game console 52 via control interface logic 178. Thus, each of the internal

integrated circuits in the expansion device 95 are controlled by the main processor (CPU) 100 in the console 52 through the control interface logic component 178.

FIG. 3 shows a keyboard and game controllers connected to the video game console 52. In accordance with one embodiment of the present invention, the wired keyboard connection may be replaced by, for example, an infrared wireless keyboard link. The keyboard data may be input via the RF input to video circuitry 176.

Control and interface logic 178, which may be implemented in a variety of different ways, includes the control and video game system interface logic for expansion device components including mass storage device 174, video circuitry 176, modem 186, and audio circuitry 188. In the security system embodiment described and claimed herein, control and interface logic 178 is implemented to include the media engine related components shown and described in conjunction with FIG. 13 which will be explained in detail below.

In accordance with an exemplary embodiment of the present invention, control and interface logic 178 includes a bus interface 179 for controlling communication over the address/data bus of the video game system shown in FIG. 3. Bus interface 179 receives direct memory access (DMA) read/write commands over the video game system console's address/data bus and responds to such commands by supplying the requested data or by transferring data to an identified component. Thus, large data blocks may be transferred by control and interface logic 178 in DMA mode to, for example, mass storage device 174. The control and interface logic 178 receives a DMA request with appropriate addresses and transfers data between the video game console and expansion device 95 in response to read or write clock signals. Data is typically obtained by control and interface logic 178 from RAM 181, boot ROM 182, mass storage device 174 and transferred to the video game console main memory RD RAM 300 (FIG. 2).

The expansion device 95 also includes an audio section 188 controlled by control and interface logic 178. The audio circuitry 188 receives and may, for example, be utilized to mix the left and right audio received from video game console 52 with the audio output of the tuner resident in the video section 176. The audio section 188 receives audio information from a microphone input, digitizes such audio input and, for example, may couple such audio information to the video game system console 52. Audio section 188 includes an audio output (L/R) and a headphone audio output (L/R).

Expansion device **95** also includes a modem **186** which is controlled by control and interface logic **178**. Data and control signals may be coupled to and from modem **186** and, for example, video game console **52** via control and interface logic **178**. Modem **186** is coupled to audio section **188** to permit voice data to be input and output to the modem. As is conventional, modem **186** interfaces with the telephone line for receiving and transmitting information. Modem **186** may, for example, be any of a wide range of modems such as a V.34 or V.90 telephone modem, an ADSL modem, a cable modem, or, wireless modem.

Control and Interface logic 178 may additionally include a digital signal processor (DSP) and an associated first in, first out (FIFO) stack for use in controlling modem 186. Modem 186 requires hand-shaking operations for data exchange which is controlled by the digital signal processor. 65 The FIFO buffers data communicated to and from modem 186. The modem DSP interrupts the video game console 52

14

via the console's control and status registers to inform the video game console 52 that modem data is ready for processing.

Control and interface logic **178** is also coupled to RAM **181**. RAM **181** provides buffer space for incoming modem data and disk sectors, for example, from mass storage device **174** during read/write operations.

Mass storage device 174 is preferably a fixed hard disk drive, but may, for example, be a removable hard disk drive. The storage device 174 may alternatively be some other high-capacity media such as Digital Versatile Disc (DVD) RAM. Alternatively, mass storage device may be implemented by a high capacity floppy disk or high capacity flash memory module. Mass storage device 174 stores a network browser program, the expansion device operating system, and all expansion device application programs. Mass storage device 174 also stores information downloaded to expansion device 95 from the Internet, such as, for example, video games and other application programs. Mass storage device 174 is controlled by an associated disk controller in control and interface logic 178 which receives control signals from the video game console 52 address/data bus.

Both the disk controller and modem controller, for example, have access to the same video game system 52 RAM/ROM space to form a unified memory structure. In an exemplary embodiment, both controllers share the memory resources and transfer memory between each other and transfer data to the video game system host. The memory subsystem requires a minimum bandwidth that is high enough to support concurrent access for all systems that have memory access. This combined architecture allows for flexible buffer schemes such as FIFOs and LIFOs. As indicated above, data may be downloaded directly to disk 174 without any host CPU action through DMA operation. Tasks may also be distributed across different processors using the unified memory scheme shown in FIG. 2. To permit the disk controller and modem controller to have concurrent access to RDRAM 300, a time multiplexed access scheme may be utilized. For example, each of the controllers may be assigned a time slice for reading from and writing to RDRAM 300. The memory speed needs to be sufficiently high enough so that concurrent access for all systems requiring memory access may be accomplished.

Control and interface logic 178 receives and couples control information from the console 52 address/data bus to video circuitry 176 such as, for example, size information for picture-in-picture displays, overlay information, and information for changing the expansion device tuner channel. The video section 176 transfers video information to, for example, video game system console 52 via the control interface and logic section 178. In this fashion, an image may be captured from the video RF input and forwarded to the video game console via the address/data bus. Intercast data carried in the vertical and/or horizontal blanking intervals may bidirectionally flow between the control interface logic 178 and video game system console 52 for a variety of purposes. In accordance with one exemplary embodiment, antipiracy features may be built into the system by monitoring the vertical blanking interval data received via the video signal and reinserting data at the output of the signal designed to prevent pirating.

Intercast data in the form of HTML information may be fed to the video game system console which forwards such information to an associated browser stored in mass storage device 174. Alternatively, program TV guide information may be fed to the video game system console. In this

fashion, TV guide information received over the Internet may in turn be stored in mass storage device 174 as the current TV guide. If a TV guide application program is resident in mass storage device 174, the current TV guide information will be utilizable by the user to, for example, identify and tune to a desired television program.

Expansion device 95 additionally includes infrared control circuitry 184 for receiving infrared input and coupling such infrared input to control and interface logic 178, which, in turn, couples such information to video game system console 52 or to video circuitry 176 for changing the TV channel via the tuner embodied in the video section 176 or via an IR transmitter. Thus, channel changing may occur under the control of control and interface logic 178 and the video section 176 tuner, even if the video game system console is in the process of controlling game play. Alternatively, the remote infrared control input may be utilized to change the TV channel under the control of the video game system console During game play, a channel may be changed, for example, in picture-in-picture mode  $\ ^{20}$ under the control of the expansion device's control and interface logic 178 and the video section's tuner. The infrared output is utilized, for example, to control via video game console 52's processor, channel changing of an external device, such as a cable box or VCR.

Boot ROM 182 is utilized during system startup and stores information for generating initial screen and other initialization data. Boot ROM 182 may also include system diagnostic software to, for example, ensure that mass storage device 174 is operational on startup. Boot ROM 182 will initiate processing from the program that is stored in a prescribed address of ROM 76 in the game cartridge 54 when the game cartridge 54 is attached to the console 52; and it will initiate processing from the program that is stored at a prescribed address of the hard disk 174 when the game cartridge 54 is not attached to the console 52. In accordance with an exemplary embodiment, when the game cartridge 54 is attached, the game cartridge 54 is given priority. Thus, by using a boot-strap ROM that stores the startup program, the system can be started by giving the program in the cartridge priority, and thereby starting the program in accordance with the program stored in the cartridge ROM when a cartridge is attached to the video game device; and in accordance with a program stored in the hard disk when no cartridge is attached.

Expansion device 95 also includes a security processor 180. Exemplary security operations performed in accordance with an illustrative embodiment of the present invention are described further below. As indicated above, serial peripheral interface 138 in FIG. 2 includes a processor which performs security tasks and which communicates with security processor 180. This pair of security processors each perform an authentication/security check. If the authentication/security check is not successful, the system is held in a reset state.

Expansion device 95 also includes a real time clock 190. The real time clock is used to maintain time and date information, which may, for example, be used during security processing.

FIG. 4 is a further block diagram of an exemplary expansion device 95 embodiment depicting shared integrated control for the modem and mass storage device. As represented in FIG. 4, the digital signal processor (DSP) based controller 194 utilized to control hard drive 206 is also 65 utilized to control modem 196. Modem 196, which is utilized to interface with the phone lines, codec 198, which

16

interfaces with the speaker phone and microphone I/O lines, read channel control 202, motor control 204 and the write command input associated with hard drive 206 are each coupled to DSP controller 194. The DSP controller 194 includes a real time clock 190 as well as input and output for infrared control.

DSP controller 194 communicates with the video section 176 and the video game console 52 via steering logic 192. Steering logic 192 may, for example, receive address information designating the appropriate destination for transmitted information. Steering logic 192 is also coupled to boot ROM 182 shown and previously described in conjunction with FIG. 3. Security processor 180 is coupled directly to video game console 52.

The control system represented in FIG. 4 advantageously utilizes the mass storage device DSP controller to multitask to control both modem 196 and hard drive 206.

FIGS. 5A and 5B are a block diagram of video circuit 176 shown in FIGS. 3 and 4. Video module 176 includes control circuitry for generating a picture-in-picture display of the type commercially available in many high-end television sets. Additionally, video circuit 176 operates to generate overlays of one picture upon another, and alpha blending involving translucent overlays with the associated ability of scaling an image to a desired size. Video circuit 176 determines which image parts may be mixed and which are not to be mixed.

The video components are, for example, coupled via an  $I^2C$  bus, which is a conventional serial bus designed for short distance communication. It provides a simple four wire, 400K bits per second interface for external expansion. The external expansion may be accomplished with an  $I^2C$  port which may include printers, keyboards, mice, etc. and which may be used to control external video devices, such as tuners and picture-in-picture devices.

As shown in FIG. 5A, video circuitry 176 receives a complete NTSC signal and the SVIDEO signal output from video game system console 52 (FIG. 3). The SVIDEO signal is input via the Video Game Y and Video Game C inputs. Additionally, as shown in FIG. 5A, a broadcast TV signal is received and coupled to the video circuit's tuner 248, which outputs a baseband signal. Tuner 248 is preferably a 120 channel cable ready tuner having high signal quality. A 45 baseband video signal also may be received by video circuit 176 and coupled to an input pin via the video game system 50 or, for example, from the output of a VCR (not shown), Direct Satellite box or a cable box. The baseband signal, an SVIDEO input signal and the output of tuner 248 are coupled to the inputs of multiplexer 247. Upon receipt of a control signal from, for example, control registers 263, one of these three multiplexer input signals is coupled to analog to digital converter 258, whose output is coupled to NTSC decoder 252.

As shown in FIG. 5A, the received signals are coupled to, for example, 8 bit analog to digital (ADC) converters 254, 256 and 258, whose outputs are in turn coupled to conventional NTSC decoders 250 and 252. The output of NTSC decoders 250 and 252 are coupled to noise processing filters 251 and 253, respectively. The output of filter 251, filter 253 and the signal received via input pin I<sup>2</sup>C are coupled to a picture-in-picture generating circuit 260 which is described further below in conjunction with FIGS. 6A and 6B.

In accordance with one exemplary embodiment of the present invention, control of the video circuitry 176 may be accomplished by control signals transmitted via the I<sup>2</sup>C input. For example, such control signals may be utilized

under control of the video game console processor to set up the control registers 263, to obtain status information about the video circuitry 176, and to transfer frame buffer vertical blanking interval data to the video circuitry 176. Alternatively, such control functions may be controlled in response to signals transmitted over the video game system address/data bus. The I<sup>2</sup>C pin may be utilized to, for example, query tuner 248, to determine whether there is a signal on a particular channel that has been set (to indicate whether the desired channel has been locked on). The I<sup>2</sup>C input may be used to control tuner 248, volume control 249, and modulator 61 and bypass switch 63 shown in FIG. 1C.

Picture-in-picture generating circuit 260 may operate in various programmable modes. For example, it may capture an input picture image and store it in SDRAM 261. Alternatively, in accordance with an exemplary embodiment, picture-in-picture generating circuit may digitally "mix" two of its inputs together as instructed based upon the output of control registers 263. Picture-in-picture generating circuit preferably operates to perform picture composing operations to generate a composite picture by partially overwriting picture image data from one source with composite picture data from another source. Such image mixing typically utilizes SDRAM 261 in that a received signal is mixed with a previously received and stored signal resident in SDRAM 261 for time-base correction purposes.

In mixing operations where one image is overlayed on another, chroma key processing may be utilized. In chroma key image processing, an image is generated by, for example, the video game system 50 having a background of a predetermined key color. A second image is generated and the two are mixed together in an overlay display as is explained further in detail below.

Instead of an overlaying operation, an alpha blending operation may be controlled by setting a particular bit in the mode control register shown as one of the control registers 263. Such a blending operation may, for example, be used to generate a display where the channel number or information about a particular show is generated at the bottom portion of the television screen.